Baya- AI Enabled SoC Intgration Platform, IP-XACT 1685, UPF, Verilog and VHDL Parsers, Translators & Converters, Datamodel and Re-Writers

Baya - Auto Integration of SoC Components with IP-XACT & Tcl API

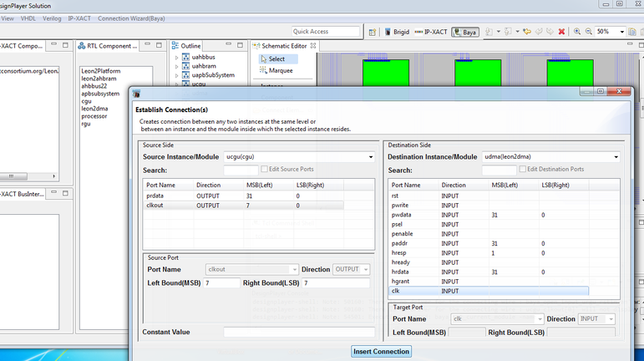

EDAUtils provides a comprehensive SoC Integration Platform, named Baya, to assemble IPs defined in IP-XACT, Verilog or VHDL. Baya offers an excellent GUI with Commands, Tool Boxes and Connection Wizard to import IPs, instantiate components and build connection among the same. Baya comes with a very rich set of Tcl commands- there are around 200 high level Tcl commands and hundreds of low level APIs for the advanced users.

Over the past few years, the consumer revolution has led to a convergence of applications on a single device and this trend is continuing with the growing market of smartphones where the target is enable the consumers to read e-mail, text friends, create spreadsheets and documents, watch YouTube, play video games, listen to music, take pictures, store them, get directions. To meet this growing consumer demad, today we have SoCs that contain hundreds of IP blocks and cores that can come from other departments, other divisions or even bought as commercial IP and integrating these IPs requres strong SoC Integration solution.

Comes

with 200+ high level Tcl commands around SoC platform assembly

Easy

to get started

Supports

Adhoc and Interface based connections

Supports

Autoconnections

Maintains

a connectivity database with advance queries

Supports

a variety of SoC integration Methodologies

XLS/CSV

Based connections

Port-to-Port

Adhoc connections

IP-XACT

and System Verilog Interface based connections

Hierarchy

Manipulation to create Power Domain, Voltage Domain, comply with

Floor planning

Associate

the IP-XACT memory maps with the SoC component instances

Supports

Glue-Logic insertion

Spare

port insertion through hierarchies

Supports

automatic creation of the top module and it's ports based upon specified rule

Creates

empty module corresponding to the instances

Utility

to compare Entities, Modules and IP-XACT Components

IP-XACT

Coherency checker

Tcl

command to save the database as VHDL, Verilog and IP-XACT Design

Reports

Design Maturity in terms of % of unconnected ports

Unix

like commands( e.g. ls, cd, rename etc. ) to browse the design

Powerful

GUI

Displays

components from the IP-XACT Library and Verilog

Displays

the associated bus interfaces in a component

Hierarchical

view of Registers and BitFields.

Easy

way to capture connectivity intent.

Drag

an drop modules from the library to instantiate